### МИНИСТЕРСТВО ОБЩЕГО И ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

# МОСКОВСКИЙ ГОСУДАРСТВЕННЫЙ ИНСТИТУТ РАДИОТЕХНИКИ, ЭЛЕКТРОНИКИ И АВТОМАТИКИ (ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ)

## КУРСОВОЙ ПРОЕКТ

по предмету СХЕМОТЕХНИКА

Выполнил студент гр. ВВ-4-07 Романычев И.А.

### СОДЕРЖАНИЕ КУРСОВОГО ПРОЕКТА

| Техническое задание                                                                                                                       | .3        |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1. Анализ существующих структур дешифраторов                                                                                              |           |

| 1.1. Линейный дешифратор                                                                                                                  | .4        |

| 1.2. Каскадные дешифраторы                                                                                                                | .5        |

| 1.2.1. Каскадные дешифраторы с принципом построения на много входов                                                                       | из        |

| микросхем с меньшим числом входов                                                                                                         | .5        |

| 1.2.2. Пирамидальный дешифратор                                                                                                           | .6        |

| 1.2.3. Прямоугольный дешифратор                                                                                                           | 6         |

| 1.3. Анализ рассмотренных типов дешифраторов                                                                                              |           |

| 1.4. Анализ технического задания на курсовой проект                                                                                       | 8         |

| 2. Разработка функциональной и структурной схем проектируемого узла                                                                       |           |

| 2.1. Разработка функциональной схемы                                                                                                      | 8         |

| 2.2. Описание работы функциональной схемы                                                                                                 |           |

| 2.3. Выбор системы элементов                                                                                                              |           |

| 2.4. Характеристики ИМС                                                                                                                   | .11       |

| 2.5. Описание работы базового логического элемента ИС 1533 серии                                                                          |           |

| 2.6. Описание работы базового логического элемента ИС 531 серии                                                                           |           |

| 3. Разработка принципиальной электрической схемы проектируемого узла 3.1. Описание принципиальной электрической схемы проектируемого узла | .13<br>14 |

| 4. Конструкторская часть                                                                                                                  |           |

| 4.1. Технология изготовления печатной платы                                                                                               | .17       |

| 4.1.1. Технология изготовления печатной платы по субтрактивн                                                                              |           |

| технологии                                                                                                                                |           |

| 4.2. Особенности монтажа на односторонних печатных платах                                                                                 |           |

| 4.3. Конструкция узла                                                                                                                     |           |

| 4.4. Размещение элементов на плате                                                                                                        | .21       |

| 5. Графическая часть проекта                                                                                                              | 22        |

| Список используемой литературы                                                                                                            | 28        |

### ТЕХНИЧЕСКОЕ ЗАДАНИЕ

### Разработать дешифратор:

- 1.Основание для разработки изделия: на основании учебного плана.

- 2. Назначение и область применения: Дешифратором или декодером (decoder) чаще всего называют кодирующее устройство, преобразующее двоичный код в унарный. Из всех m выходов дешифратора активный уровень имеется только на одном, а именно на том, номер которого равен поданному на вход двоичному числу. На всех остальных выходах дешифратора уровни напряжения неактивные.

Декодер используют, когда нужно обращаться к различным цифровым устройствам, и при этом номер устройства — его адрес — представлен двоичным кодом. Входы декодера (их иногда называют адресными входами) часто нумеруют не порядковыми номерами, а в соответствии с весами двоичных разрядов, т.е. не 1, 2, 3, 4, 5 а 1, 2, 4, 8, 16. Число входов и выходов декодера указывают таким образом: декодер  $4 \rightarrow 16$  (читается "четыре в шестнадцать").

- **3. Условия эксплуатации:** Разрабатываемый дешифратор 4→16 должен эксплуатироваться при температуре окружающей среды 18°C.

- 4. Общие и частные технические требования:

Тактовая частота  $f_{\text{такт.}}$  (не менее) 40 МГц Потребляемая мощность  $P_{\text{потр.}}$  (не более) 2,5 Вт Число входов n=4 Число выходов m=16 Печатная плата — односторонняя.

### 1. АНАЛИЗ СУЩЕСТВУЮЩИХ СТРУКТУР ДЕШИФРАТОРОВ

### 1.1. Линейный дешифратор.

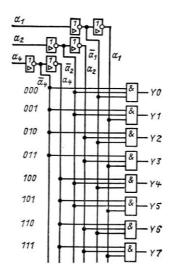

Основной объем его оборудования составляют в общем случае m n-входовых элементов И. Кроме того, к оборудованию дешифратора обычно относят n инверторов входных переменных и n буферных входных усилителей, обычно инвертирующих, что характерно для интегральной технологии.

Назначение буферных усилителей—свести к единице кратность нагрузки, которую представляет дешифратор для источника сигнала. Иначе каждый источник сигнала, как следует из рисунка, будет нагружен весьма существенно — на m/2 входов элементов И.

Если дешифратор состоит из элементов И-НЕ, то на его выходах будут отрабатываться не сами функции Y<sub>i</sub>, а их инверсии, т.е. активным уровнем выхода будет низкий. Ликвидировать инверсии на выходах можно или подключив инверторы, или построив дешифратор по двойственной схеме — на элементах ИЛИ-НЕ. Число входных инверторов и буферных усилителей при этом не изменится.

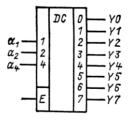

Дешифраторы часто имеют разрешающий (управляющий, стробирующий) вход E (от enable—давать возможность). При E=1 дешифратор работает как обычно, при E=0 на всех выходах устанавливаются неактивные уровни независимо от поступившего кода адреса. Вход E часто выполняют инверсным. Дешифратор, имеющий разрешающий вход, иногда называют декодердемультиплексор и на условном обозначении вместо символа DC используют символ DX.

На рисунке ниже показан вариант построения разрешающего входа, когда сигнал Е воздействует непосредственно на все дешифрирующие элементы. Этот вариант требует увеличения на единицу числа входов дешифрирующих элементов, но не вносит дополнительной задержки.

На рисунке ниже показан другой вариант, основанный на том, что в дешифраторе не найдется ни одного дешифрирующего элемента, к которому любая переменная не была бы подключена или в своей прямой, или в инверсной форме. Поэтому если и в прямой, и в инверсный тракты любой входной переменной поставить элементы И и завести на них сигналы Е, то при E=0 будут заперты абсолютно все конъюнкторы, подключенные к выходам.

На рисунке показано воздействие сигнала E на среднюю переменную, чтобы не создавалось ложного впечатления, что запирать дешифратор надо обязательно или по старшей, или по младшей переменной.

Способ управления по одной из входных переменных экономичен по оборудованию, но увеличивает задержку дешифратора.

Линейные дешифраторы изготавливаются в виде ИМС на 2...4 входа.

### 1.2. Каскадные дешифраторы.

## 1.2.1. Каскадные дешифраторы с принципом построения на много выходов из микросхем дешифраторов с меньшим числом выходов.

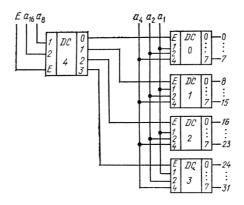

На рисунке ниже представлена группа из пяти дешифраторов, соединенных в два каскада. Вся группа работает как дешифратор  $5 \rightarrow 32$ .

Два старших разряда адреса а<sub>16</sub> и а<sub>8</sub> расшифровываются дешифратором 2-4 DC4, который по входам Е управляет четырьмя дешифраторами 3-8 второго каскада. Младшие разряды адреса

а<sub>4</sub>, а<sub>2</sub>, а<sub>1</sub> поступают на все дешифраторы второго каскада, но открытым по входу Е оказывается лишь один из них. Ему и будет принадлежать единственный из всех 32 возбужденный выход.

Принцип используется при построении дешифраторов на много выходов из микросхем дешифраторов с меньшим числом выходов.

В рассмотренном примере 5-разрядный адрес был разбит на две группы в 2 и 3 разряда, и это определило структуру всей схемы. В общем случае многоразрядный адрес можно разбить на группы различными способами, и каждому способу будет соответствовать свой вариант схемы многокаскадного (не обязательно двухкаскадного) дешифратора.

Варианты будут отличаться задержкой и аппаратурными затратами, и можно ставить задачу выбора оптимальной в заданной серии элементов структуры.

### 1.2.2. Пирамидальный дешифратор.

В предельном случае при числе каскадов, равном разрядности адреса, получается пирамидальный дешифратор, имеющий максимально возможную задержку.

Достоинством его является использование только двухвходовых элементов И, что определило его широкое распространение на заре цифровой техники, и с тех пор он, как сорняк, неистребим в литературе.

В современных многовходовых логических базисах пирамидальная схема дешифратора не выдерживает конкуренции с другими структурами даже по оборудованию, не говоря уже о задержке.

### 1.2.3. Прямоугольный дешифратор.

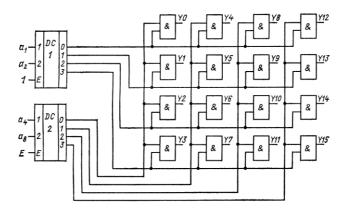

На рисунке показан двухкаскадный дешифратор 4→16. второй каскад, которого собран по схеме прямоугольного дешифратора.

Разряды адреса разбиты на две группы, каждая из которых независимо от другой расшифровывается своим дешифратором первого каскада DC1 и DC2, При любой комбинации значений входных переменных оказываются выбранными одна строка и один столбец сетки, в узлах которой расположены элементы И второй ступени. В результате каждый входной набор возбуждает выход единственного соответствующего ему элемента И. Такую сетку из элементов И и называют прямоугольным или матричным дешифратором.

При использовании во второй ступени элементов И-НЕ выходы дешифратора будут инверсными. Их можно сделать прямыми, построив сетку второго каскада по двойственному варианту, на элементах ИЛИ-НЕ; тогда инверсными должны быть выходы дешифраторов первого каскада.

Делить разряды адреса между DC1 и DC2 нужно по возможности поровну: чем ближе прямоугольник второго каскада к квадрату, тем при том же числе выходных элементов И меньше сумма его строк и столбцов, т. е. меньше число выходов дешифраторов первого каскада. В качестве входа Е всего двухкаскадного дешифратора удобно использовать разрешающий вход одного из дешифраторов первого каскада. При этом запираются или все строки, или все столбцы.

### 1.3. Анализ рассмотренных типов дешифраторов.

Целесообразно сравнить рассмотренные типы дешифраторов по величине задержки и аппаратурным затратам. Задержка минимальна для линейного дешифратора и в пределе может быть равна (2—3)t в зависимости от числа ступеней инверторов-усилителей.

При включении линейных дешифраторов в несколько каскадов задержки всех каскадов складываются.

Чем больше число выходов дешифратора, тем большая доля оборудования сосредоточена в элементах И самого последнего каскада. Число элементов предпоследнего каскада уже в несколько раз меньше, чем последнего, а предыдущих — тем более. Число элементов И последнего каскада дешифратора любого типа всегда равно числу его выходов, поэтому в первом приближении аппаратурные затраты дешифраторов различных типов соотносятся как аппаратурные затраты их элементов И последнего каскада. Они и определяют основную разницу: у линейного дешифратора число входов каждого элемента И последнего (и единственного) каскада равно п (п—число адресных входов), у каскадного оно зависит от способа разбиения на группы, однако оно всегда меньше п, но больше двух, у прямоугольного оно равно двум — минимально возможному числу. Поэтому при большом числе выходов (сотни и более) прямоугольный дешифратор — самый экономичный по оборудованию, чем и объясняется его широкое применение в БИС памяти. При уменьшении числа выходов до нескольких десятков первенство по экономичности переходит к каскадным дешифраторам, а при малом числе выходов самым экономичным (а к тому же и самым быстрым) оказывается линейный дешифратор.

Приведенные оценки справедливы лишь для дешифраторов, построенных непосредственно из логических элементов, например при разработке схемы матричной БИС.

При проектировании же блоков из готовых микросхем, когда затраты оборудования оцениваются не числом элементов, а числом корпусов, даже большие дешифраторы экономичнее строить по каскадному принципу, набирая их из микросхем небольших дешифраторов на 8 или 16 выходов.

Дешифраторы, выпускаемые в виде отдельных микросхем, имеют буквенное обозначение ИД. В сериях ТТЛ, в которых элементы И-НЕ наиболее технологичны, дешифраторы обычно имеют инверсные выходы, т. е. активный низкий уровень выходного сигнала. В КМДП-сериях, где элементы ИЛИ-НЕ не менее технологичны, чем И-НЕ, дешифраторы чаще имеют прямые выходы.

Стремление возможно полнее использовать выводы типовых корпусов определяет размеры декодеров, выпускаемых в виде СИС. Обычно это  $3 \rightarrow 8$ ,  $4 \rightarrow 10$ , сдвоенный  $2 \rightarrow 4$ , а также  $4 \rightarrow 16$ , но уже в корпусе с 24 выводами.

Часто в микросхемах дешифраторов делают несколько разрешающих входов, а разрешающей комбинацией является их конъюнкция. При этом удобно наращивать дешифраторы, используя каскадный принцип и строя первый каскад дешифрации не на отдельном специальном дешифраторе, а собирая его из конъюнкторов разрешающих входов.

### 1.4. Анализ технического задания на курсовой проект.

Разрабатываемый дешифратор должен соответствовать следующим параметрам:

Тактовая частота f<sub>такт.</sub> (не менее) 40 МГц Потребляемая мощность Р<sub>потр.</sub>(не более) 2,5 Вт Температура окружающей среды 18<sup>0</sup>C Разрядность входа 4 Печатная плата – односторонняя.

Выводы: С точки зрения заданного быстродействия допустимо использование элементов ТТЛШ или элементов ЭСЛ.

### 2. РАЗРАБОТКА ФУНКЦИОНАЛЬНОЙ И СТРУКТУРНОЙ СХЕМ ПРОЕКТИРУЕМОГО УЗЛА

### 2.1. Разработка функциональной схемы.

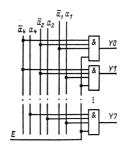

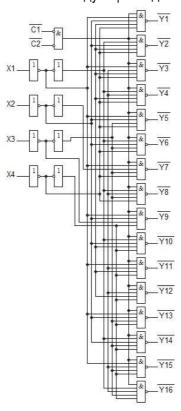

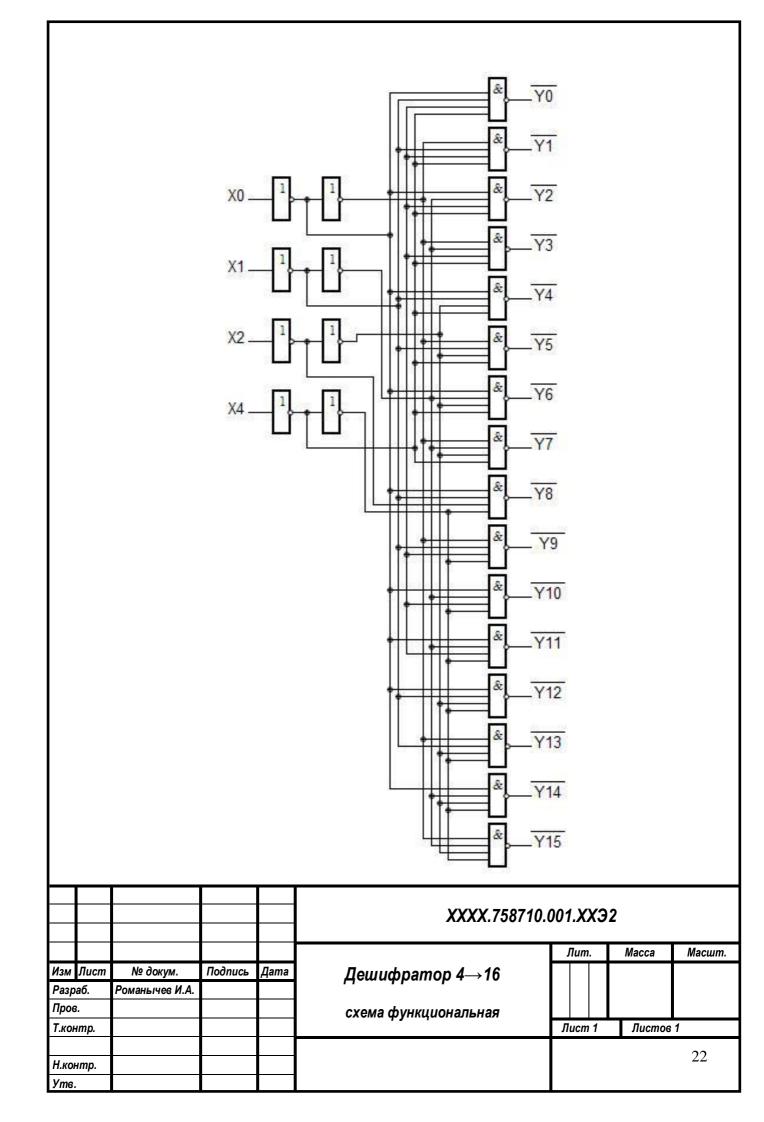

Предлагается для построения дешифратора 4—16 использовать схему, реализованную на КР1533ИДЗ. Функциональная схема ИМС имеет следующий вид:

Т.к. не бывает логических элементов 5И-НЕ, реализуем эту схему без входов стробирования. Кроме того, нагрузочная способность ИМС, как правило, не превышает 10, данное условие будет соблюдено при использовании асинхронного дешифратора, представленного на

чертеже XXXX.758710.001.XXЭ2. Активными выходами проектируемого дешифратора будут инверсные т.к. СДНФ по таблице истинности дешифратора строится легко, но на используемых логических элементах ИМС малой степени интеграции реализовать проблематично, поэтому для построения дешифратора используется следующая таблица:

| X4 | X2 | X1 | X0 | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | Y8 | Y9 | Y10 | Y11 | Y12 | Y13 | Y14 | Y15 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 1   | 1   | 1   | 1   |

| 0  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 1   | 1   | 1   | 1   |

| 0  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 1   | 1   | 1   | 1   |

| 0  | 0  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 1   | 1   | 1   | 1   |

| 0  | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 1   | 1   | 1   | 1   |

| 0  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1   | 1   | 1   | 1   | 1   | 1   |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1   | 1   | 1   | 1   | 1   | 1   |

| 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 1   | 1   | 1   | 1   | 1   | 1   |

| 1  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1   | 1   | 1   | 1   | 1   | 1   |

| 1  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1   | 1   | 1   | 1   | 1   | 1   |

| 1  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0   | 1   | 1   | 1   | 1   | 1   |

| 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 0   | 1   | 1   | 1   | 1   |

| 1  | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 0   | 1   | 1   | 1   |

| 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 1   | 0   | 1   | 1   |

| 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 1   | 1   | 0   | 1   |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 1   | 1   | 1   | 0   |

По таблице записываем СКНФ, т.к. из нее удобно строить схему в базисе И-НЕ, преобразования производим по формулам де Моргана:

$$Y0 = X0 + X1 + X2 + X4 = \overline{X0} \cdot \overline{X1} \cdot \overline{X2} \cdot \overline{X4}$$

$$Y1 = \overline{X0} + X1 + X2 + X4 = \overline{X0} \cdot \overline{X1} \cdot \overline{X2} \cdot \overline{X4}$$

$$Y2 = X0 + \overline{X1} + X2 + X4 = \overline{X0} \cdot X1 \cdot \overline{X2} \cdot \overline{X4}$$

$$Y3 = \overline{X0} + \overline{X1} + X2 + X4 = \overline{X0} \cdot \overline{X1} \cdot \overline{X2} \cdot \overline{X4}$$

$$Y4 = X0 + X1 + \overline{X2} + X4 = \overline{X0} \cdot \overline{X1} \cdot X2 \cdot \overline{X4}$$

$$Y5 = \overline{X0} + X1 + \overline{X2} + X4 = \overline{X0} \cdot \overline{X1} \cdot X2 \cdot \overline{X4}$$

$$Y6 = X0 + \overline{X1} + \overline{X2} + X4 = \overline{X0} \cdot \overline{X1} \cdot X2 \cdot \overline{X4}$$

$$Y7 = \overline{X0} + \overline{X1} + \overline{X2} + X4 = \overline{X0} \cdot \overline{X1} \cdot \overline{X2} \cdot \overline{X4}$$

$$Y8 = X0 + X1 + X2 + \overline{X4} = \overline{X0} \cdot \overline{X1} \cdot \overline{X2} \cdot \overline{X4}$$

$$Y9 = \overline{X0} + X1 + X2 + \overline{X4} = \overline{X0} \cdot \overline{X1} \cdot \overline{X2} \cdot \overline{X4}$$

$$Y10 = X0 + \overline{X1} + X2 + \overline{X4} = \overline{X0} \cdot \overline{X1} \cdot \overline{X2} \cdot \overline{X4}$$

$$Y11 = \overline{X0} + \overline{X1} + X2 + \overline{X4} = \overline{X0} \cdot \overline{X1} \cdot \overline{X2} \cdot \overline{X4}$$

$$Y12 = X0 + X1 + \overline{X2} + \overline{X4} = \overline{X0} \cdot \overline{X1} \cdot \overline{X2} \cdot \overline{X4}$$

$$Y13 = \overline{X0} + X1 + \overline{X2} + \overline{X4} = \overline{X0} \cdot \overline{X1} \cdot \overline{X2} \cdot \overline{X4}$$

$$Y14 = X0 + \overline{X1} + \overline{X2} + \overline{X4} = \overline{X0} \cdot \overline{X1} \cdot \overline{X2} \cdot \overline{X4}$$

$$Y15 = \overline{X0} + \overline{X1} + \overline{X2} + \overline{X4} = \overline{X0} \cdot \overline{X1} \cdot \overline{X2} \cdot \overline{X4}$$

### 2.2. Описание работы функциональной схемы.

На чертеже XXXX.758710.001.XXЭ2 представлена схема дешифратора 4→16. Особенность схемы: дешифратор не является синхронным. Это не является недостатком схемы: т.к. подключенный к выходам дешифратора функциональный элемент можно разработать со стробированием (т.е. с разрешением считывания управляющего сигнала). Дешифратор является линейным, описан в п.1.1 курсового проекта.

<u>Обоснование выбора схемы:</u> Линейный дешифратор наиболее подходит для реализации, т.к. он экономичен по оборудованию и имеет минимальную задержку.

### 2.3. Выбор системы элементов.

Характеристики ТТЛШ, КМОП и ЭСЛ приведены в таблице:

| Параметры | U <sub>пит.</sub> | Р <sub>потр.</sub><br>[Л/Э] | N <sub>0</sub> | U <sup>1</sup> | Т <sub>з.ср.</sub> [Л/Э] |

|-----------|-------------------|-----------------------------|----------------|----------------|--------------------------|

| ТТЛШ      | +5 B              | 19 mВт                      | 0,4 B          | 2,5 B          | >3 нс                    |

| КМОП      | +3+15 B           | 0,4 mkВт                    | 0,010,05 B*    | 4,999,99 B*    | >50 нс                   |

| ЭСЛ       | -5,2 B            | 30 mВт                      | -0,9 B         | -1,8 B         | <2 нс                    |

<sup>\*</sup> Для микросхем 561 серии.

#### Выводы:

- 1. Элементы КМОП не отвечают заданному быстродействию.

- 2. Элементы ЭСЛ имеют малую помехоустойчивость, к тому же все логические уровни имеют место в отрицательной области потенциалов. Такие логические уровни непосредственно не совместимы со схемами КМОП и ТТЛ (ТТЛШ), что считается большим недостатком.

- 3.Элементы ТТЛШ соответствуют заданному быстродействию.

### 2.4. Характеристики ИМС.

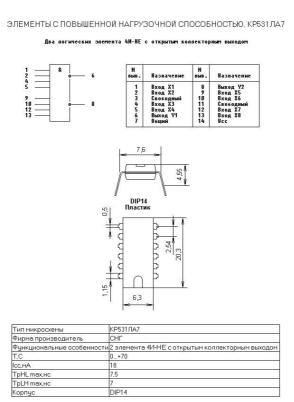

<u>Обоснование выбора ИМС:</u> Выбираем в качестве инверторов ИМС КР1533ЛН1 из-за низкой мощности потребления и достаточно высокого быстродействия.

В качестве элементов 4И-НЕ выбираем ИМС КР531ЛА7 Обоснование выбора ИМС: невысокая мощность потребления и высокое быстродействие.

DIP14

TpLH max.нс

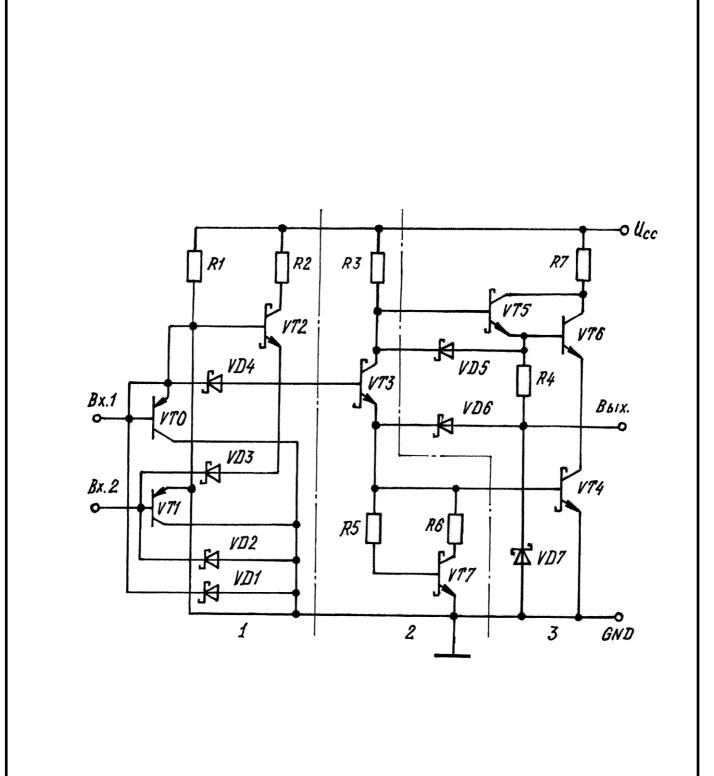

### 2.5. Описание работы базового элемента ТТЛШ серии 1533.

Электрическая принципиальная схема базового ЛЭ ИС 1533 приведена на чертеже XXXX.758710.002.XXЭ3 (см. графическую часть проекта).

Базовый ЛЭ ИС 1533 содержит три основных каскада: входной, включающий транзисторы VT1, VT2, диод VD1 и резисторы R1, R2; фазоразделительный, выполненный на резисторах R3, R5, R6, транзисторах VT3, VT7 и диодах VD2, VD3; выходной усилитель на транзисторах VT4 — VT6 и резисторах R4, R7.

При низком напряжении на входе микросхемы на базе транзистора VT2 поддерживается низкое напряжение, которого недостаточно для его отпирания. Транзисторы VT2 — VT4 закрыты. Высокое напряжение на входе транзистора VT5 открывает его, а также транзистор VT6. На выходе схемы устанавливается напряжение высокого уровня.

При высоком напряжении на входе схемы эмиттерный переход транзистора VT1 закрыт, и ток через резистор R1 поступает в базу транзистора VT2, который отпирается и соответственно открываются VT3 и VT4. Транзисторы VT5 и VT6 закрыты, и на выходе схемы устанавливается напряжение низкого уровня.

С помощью использования сложного выходного каскада на транзисторах VT4 — VT6 и диодах VD2 и VD3 в микросхеме достигается увеличение быстродействия из-за быстрого заряда емкостей на выходе схемы. Сложный выходной каскад обеспечивает малые времена фронтов выходного сигнала. Транзисторы VT2 и VT3 увеличивают порог переключения схемы и повышают ее помехоустойчивость. Повышению помехоустойчивости способствует и корректирующая цепочка, выполненная на транзисторе VT7 и резисторах R5 и R6.

Все транзисторы схемы, кроме VT1 и VT6, являются транзисторами Шотки. Транзистор VT6 не работает в режиме насыщения, поэтому использовать вместо него транзистор с диодом Шотки не имеет смысла. Применение диодов и транзисторов Шотки позволяет значительно уменьшить либо полностью исключить время рассасывания избыточного заряда в транзисторах схемы и повысить ее быстродействие.

Логический элемент ИС 1533 при малой мощности потребления (1 мВт/ЛЭ) имеет достаточно высокое быстродействие (типовое время задержки 4 нс/ЛЭ).

Улучшение параметров ИС 1533 достигнуто с помощью новых схемотехнических решений, уменьшения геометрических размеров транзисторов и диодов Шотки, а также с помощью технологических способов, в том числе использования тонких эпитаксиальных пленок толщиной до 2 мкм.

Серия ИС 1533 является функционально полной и содержит в своем составе счетчики, регистры, АЛУ, схемы сравнения, формирователи и т. д. Маломощные ИС 1533 нашли широкое применение в аппаратуре с жесткими требованиями по потребляемой мощности.

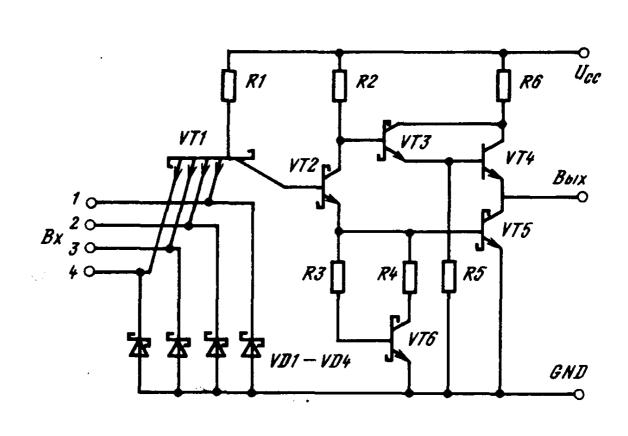

### 2.6.Описание работы базового логического элемента ИС 531 серии.

В качестве базового ЛЭ ИС КР531 использован ЛЭ типа И-НЕ. Схема ЛЭ содержит три основных каскада маломощных ТТЛШ серий. Входной каскад выполнен на многоэмиттерном транзисторе VT1, фазоразделительный — на транзисторах VT2, VT3, VT6 и резисторах R2—R5. Выходной каскад включает транзисторы VT4, VT5 и резистор R6.

При одновременной подаче на все входы многоэмиттерного транзистора напряжения высокого уровня ток резистора R1 потечет через база — коллекторный переход транзистора VT1 в базу транзистора VT2. Транзисторы VT2 и VT5 открыты и на выходе схемы устанавливается низкий уровень напряжения.

Если хотя бы на один из входов схемы подан низкий уровень напряжения, то транзисторы VT2, VT5 закрыты. Через резистор R2 течет базовый ток транзистора VT3, и на выходе микросхемы устанавливается напряжение высокого уровня.

Включение в базу выходного транзистора VT5 корректирующей цепочки (VT6, R3, R4), как и в маломощных сериях, позволяет повысить помехозащищенность микросхемы в выключенном состоянии в результате улучшения передаточной характеристики. А использование каскада Дарлингтона на транзисторах VT3 и VT4 обеспечивает почти одинаковые значения выходного сопротивления микросхемы при ее включении и выключении, что позволяет получить симметричную задержку входного сигнала.

Высокое быстродействие схемы обеспечивается выбором номиналов резисторов, уменьшением топологических размеров диодов, транзисторов, толщин эпитаксиальных пленок и использованием диффузионных процессов с более мелкими диффузионными слоями.

Базовый ЛЭ ИС КР531 при потребляемой мощности 19 мВт имеет типовое время задержки 3 нс, что позволило повысить максимальную частоту работы триггеров серии до 125 МГц.

### 3. РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ ПРОЕКТИРУЕМОГО УЗЛА

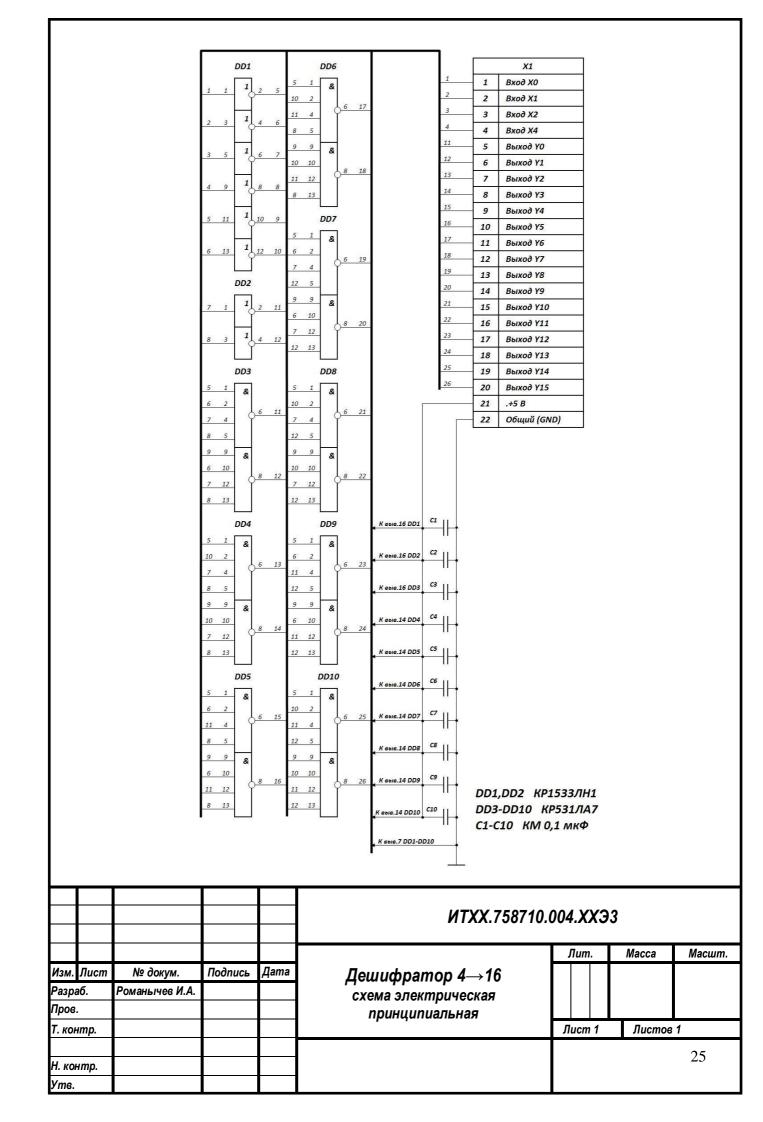

### 3.1.Описание принципиальной электрической схемы проектируемого узла.

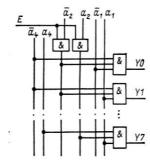

Разрабатываемый двоичный дешифратор 4—16 состоит из восьми ИМС КР531ЛА7, двух ИМС КР1533ЛН1 и десяти керамических конденсаторов емкостью 0,1 мкФ, необходимость использования которых обусловлена следующими соображениями:

Значение порога у элементов ТТЛ(ТТЛШ) близко к уровню земли, вследствие чего все это логическое семейство в известной степени подвержено влиянию помех. Так как эти логические семейства являются быстродействующими, они воспринимают короткие всплески по шине земли. Такие всплески часто возникают при быстрой смене состояний на выходах, что еще более осложняет проблему.

Биполярные ТТЛ(ТТЛШ) элементы предъявляют высокие требования к источнику питания: +5B±5% при относительно высокой мощности рассеяния. Наличие токовых всплесков в шинах питания, которые вырабатываются схемами с активной нагрузкой, как правило, требует шунтирования источника питания, в идеальном случае один конденсатор емкостью 0,1 мкФ на каждый корпус ИМС.

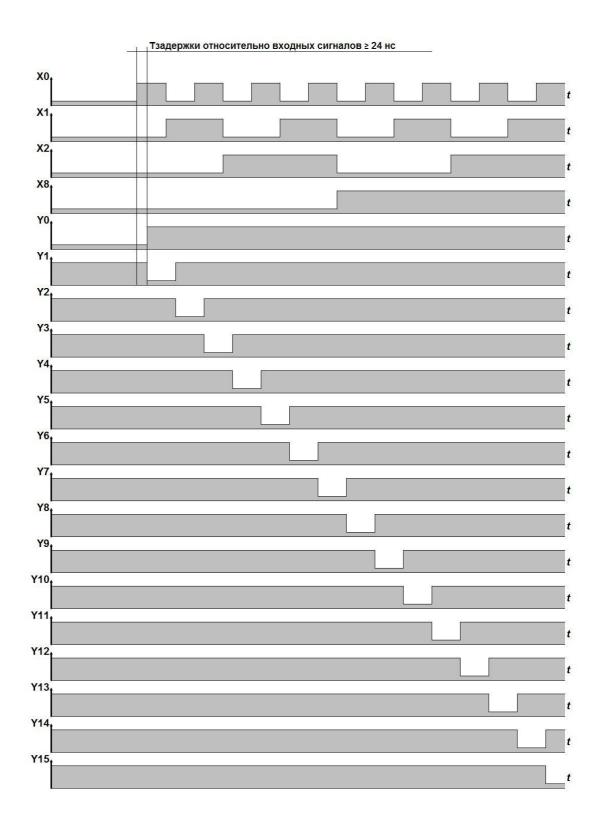

### 3.2. Временные диаграммы работы.

Если на входах дешифратора 4→16 D0-D4 уровень логического «0», то на выходе Y0 низкий уровень, который является активным. Аналогично: если на входах дешифратора D0-D4 имеется комбинация двоичного кода, то на том выходе Y0-Y15, номер которого соответствует значению двоичного входного кода, будет уровень логического «0», на остальных выходах - логической «1».

Время задержки на дешифраторе не менее 24 нс (см. расчет быстродействия).

### 3.3. Расчетная часть.

**3.3.1. Быстродействие** проектируемого двоичного дешифратора  $4 \rightarrow 16$  рассчитывается с учетом времени задержки на трех микросхемах, соединенных последовательно (КР1533ЛН1 и КР531ЛА7):

$$t_{3ad, cp.} = (t_{3ad, 1}^{10} + t_{3ad, 1}^{01}) \cdot 2 + (t_{3ad, 2}^{10} + t_{3ad, 2}^{01}) \cdot 2 + (t_{3ad, 2}^{10} + t_{3ad, 2}^{01}) \cdot 2 + (t_{3ad, 2}^{10} + t_{3ad, 2}^{10}) \cdot 2 + (t_{3ad, 2}^{$$

тогда:

быстродействие=1/  $t_{\text{зад. cp.}}$ =1/24нc=41666666 Гц

Так как расчетное быстродействие превышает заданное, то разработанная схема соответствует заданному условию.

**3.3.2.** Потребляемая мощность проектируемого двоичного дешифратора 1→16 рассчитывается как суммарная для всех ИМС, используемых в схеме, т. е. для десяти микросхем:

$$P_{\text{потр.}} = \sum P_{\text{потр.ИМС1-10}} = 0,76 \text{ BT}$$

Так как расчетная потребляемая мощность не превышает заданную, то разработанная схема соответствует данному условию.

**3.3.3. Помехоустойчивость** цифровых микросхем определяют по следующей методике. Измерив значения выходных напряжений  $U^1_{\text{вых.мин.}}$ ,  $U^0_{\text{вых.макс.}}$  и пороговых напряжений  $U^1_{\text{пор.}}$ ,  $U^0_{\text{пор.}}$ , вычисляют статическую помехоустойчивость по высокому уровню с помощью формулы:

$$U_{\text{пом.}}^{1} = |U_{\text{вых.мин.}}^{1} - U_{\text{пор.}}^{1}|$$

статическую помехоустойчивость по низкому уровню по формуле:

$$U_{\text{пом.}}^0 = |U_{\text{пор.}}^0 - U_{\text{вых.макс.}}^0|$$

и выбирают меньшее из двух полученных значений.

Помехоустойчивость проектируемого двоичного дешифратора 4—16 определяем по справочнику для микросхем серии KP531:

$$U_{\text{пом}} = 0.3 \text{ B}$$

для микросхем серии 1533:

– более высокая помехоустойчивость по сравнению с ИМС КР531.

**3.3.4. Нагрузочную способность** проектируемого двоичного дешифратора 4→16 определяем по справочнику для микросхем серий КР531 и КР1533:

$$K_{pas.} = 10.$$

## 3.3.5. Расчет рабочего значения плотности тока в проводниках на печатной плате.

Основные требования к электрическим параметрам печатных плат сформулированы в ГОСТ 23751 — 86 и отраслевых стандартах.

Для 3 класса плотности имеем:

Шаг координатной сетки 1,27 мм

Ширина проводника t=0,254 мм

Расстояние между проводниками s=0,254 мм

Ширина пояска печатной площадки b=0,1мм

Толщина фольги печатной платы  $h_{\phi}$ =70 мкм (с лужением)

Тогда:  $i=I_{pa6}/h_{tb}$ -t

За Іраб. примем значение тока в цепи питания микросхем, тогда:

$i=0,152/70\cdot10^{-3}\cdot0,254=8,55\ A/mm^2$

Для открытых печатных проводников, (т.е. не для многослойных печатных плат) предельное допустимое значение 15...30 А/мм<sup>2</sup>.

Так как расчетная плотность тока не превышает предельное допустимое значение, то разработанная печатная плата соответствует данному условию.

### 3.3.5. Расчет надежности.

Для расчета надежности для всех элементов схемы из справочника выписываются значения интенсивности отказов при работе в нормальных условиях.

| Наименование      | Интенсивность                             | Количество | Интенсивность                            |

|-------------------|-------------------------------------------|------------|------------------------------------------|

| элементов         | отказов                                   | элементов  | отказов общая                            |

| ИМС               | 0,1·10 <sup>-6</sup> час <sup>-1</sup>    | 10         | 1,0·10 <sup>-6</sup> час <sup>-1</sup>   |

| конденсаторы      | 0,002·10 <sup>-6</sup> час <sup>-1</sup>  | 10         | 0,02·10 <sup>-6</sup> час <sup>-1</sup>  |

| разъем            | 0,025·10 <sup>-6</sup> час <sup>-1</sup>  | 22         | 0,55·10 <sup>-6</sup> час <sup>-1</sup>  |

| пайки             | 0,0004·10 <sup>-6</sup> час <sup>-1</sup> | 160        | 0,064·10 <sup>-6</sup> час <sup>-1</sup> |

| Печатная<br>плата | 0,6·10 <sup>-6</sup> час <sup>-1</sup>    | 1          | 0,6·10 <sup>-6</sup> час <sup>-1</sup>   |

Суммарная интенсивность отказов( $\sum \lambda$ )=0,2234·10-5 час-1

Надежность определим по формуле:

$P(t)=e^{-(\sum \lambda)\cdot t}$

Для 100 часов работы:

P(100)=0,9997766

Для 1000 часов работы:

P(1000)=0,99776849

Для 10000 часов работы:

P(10000)=0,9779077

### 4. КОНСТРУКТОРСКАЯ ЧАСТЬ

#### 4.1. Технология изготовления печатной платы.

Печатная плата – монтажная плата для размещения пассивных и активных ЭРЭ.

Изготавливаются печатные платы на основе диэлектрика или металла, на который наносится диэлектрический слой. Рисунок содержит токоведущие дорожки, контактные площадки, пробельные места, соединительные отверстия, монтажные отверстия.

В современных печатных платах в рисунок могут входить пассивные элементы (R, C, L).

По конструктивным признакам печатные платы можно разделить на:

- 1.Однослойные, которые бывают:

- а) односторонними;

- б) двухсторонними.

- 2. Многослойные.

В настоящее время при изготовлении печатных плат достигнуты следующие параметры:

#### 1.Габаритные размеры (максимальные):

- \* 240 Х 360 мм:

- \* 400 Х 600 мм.

#### 2. Шаг координатной сетки:

- \* 2,5 мм;

- \* 1,25 мм;

- \* 0,5 мм;

- \* 0,25 мм.

#### 3. Минимальная ширина печатного проводника:

- \* 0,1 mm;

- \* 0,075 мм;

- \* 0,05 мм;

#### 4. Минимальное расстояние между печатными проводниками:

- \* 0,1 мм;

- \* 0,075 мм;

- \* 0,05 мм.

#### 5. Минимальный диаметр соединительного отверстия:

\* 0,1 мм.

#### 6. Для многослойных печатных плат количество слоев, которое можно получить:

- \* 16-24 (старая технология);

- \* 6-12; 10-20 (новая технология);

- \* до 50 слоев (японская технология).

Наибольшее распространение получили однослойные печатные платы.

### 4.1.1. Технология изготовления печатной платы по субтрактивной технологии.

Применяются следующие материалы (для односторонних печатных плат):

- 1. Гетинакс ГФ-1-35-2,0;

- 2. Стеклотекстолит фольгированный СФ-1H-50Г-1,2.

Производятся следующие технологические операции:

- 1. Проектирование заготовки печатной платы: к основному размеру прибавляется 10 мм для технологического поля, которое необходимо для:

- a) базовых отверстий (для однозначной ориентации при прохождении технологического процесса);

- б) технологических отверстий (для контроля прохождения технологического процесса);

- в) крепления пробных проводников.

После изготовления технологическое поле удаляется.

- 2. Получение заготовки из фольгированного материала применяются роликовые или дисковые ножницы, фрезерование.

- 3. Сверление всех отверстий на станке с ЧПУ.

- 4. Производится подготовка поверхностей: снимается оксидная пленка с фольги с помощью погружения заготовки в 5% раствор соляной кислоты на 5 мин., поверхность обезжиривается.

- 5. Получение изображения печатных проводников:

- а) фотоспособом заготовка покрывается специальным материалом фоторезистом, реагирующим на свет и, в зависимости от конкретной схемы изготовления фоторезист будет защищать нужные места (пробельные или печатные проводники).

- б) трафаретным способом защита с помощью трафарета и краски.

- 6. Удаление фольги: применяются травители хлористое железо Fe₂Cl₃, персульфат аммония.

- 7. Для печатных плат, имеющих разъемы необходимо получение износостойкого слоя в месте контакта:

- а) печатная плата облуживается;

- б) в местах контакта снимается ПОС химическим методом, после этого гальванически наращивается никель или кобальт (подслой), а затем электрохимически наслаивается палладий или золото.

- 8. Производится частичная герметизация изделия: печатную плату опускают в лакофлюс.

- 9. Удаляется технологическое поле.

Контроль производится на всех этапах.

#### 4.2. Особенности монтажа на односторонних печатных платах.

Одним из основных условий, обеспечивающих надежную работу РЭА, сконструированной с широким применением интегральных микросхем, является соблюдение правил по их установке, пайке и монтажу. Основными элементами конструкции узлов и блоков РЭА, позволяющими наиболее полно реализовать преимущества МС, являются печатные платы. При установке МС на печатные платы необходимо соблюдать следующие требования и условия:

- 1. установка и крепление микросхем на печатных платах должны обеспечивать их нормальную работу в условиях эксплуатации аппаратуры;

- 2. должны строго выдерживаться указанные в технической документации расстояния от корпусов МС до мест изгибов и мест пайки их выводов;

- 3. шаг установки МС на печатные платы должен быть кратен 2,5; 1,25 или 0,5 мм (в зависимости от типа корпуса и конструкции узла, блока);

- 4. должно соблюдаться линейно-многорядное (или шахматное) расположение МС, обеспечивающее наибольшую плотность их компоновки и возможность механизированной сборки узлов;

- 5. микросхемы с расстоянием между выводами, кратном 2,5 мм, должны располагаться на печатной плате таким образом, чтобы их выводы совпадали с узлами координатной сетки;

- 6. если расстояние между выводами МС не кратно 2,5 мм, они должны располагаться так, чтобы один или несколько выводов микросхемы совпадали с узлами координатной сетки;

- 7. установка и крепление микросхем должны обеспечивать доступ к любой из них и возможность их замены;

- 8. для правильной ориентации МС на печатной плате должны быть предусмотрены «ключи», определяющие положение первого вывода каждой микросхемы;

- 9. расположение и крепление МС должны обеспечивать возможность групповой пайки с последующей влагозащитой;

- 10. в случае необходимости плата с установленными МС должна быть защищена от воздействия климатических факторов.

Кроме того, при расположении MC на печатных платах при конструировании следует руководствоваться следующими положениями:

- 1. микросхемы должны быть удалены от элементов, которые при работе выделяют большое количество тепла, на расстояния, исключающие перегрев микросхем;

- 2. микросхемы недопустимо располагать в магнитных полях постоянных магнитов, трансформаторов и дросселей;

3. необходимо обеспечивать конвекцию воздуха у радиаторов элементов и элементов, выделяющих большое количество тепла.

Необходимо принимать меры, исключающие воздействие на MC статического электричества.

### 4.3. Конструкция узла.

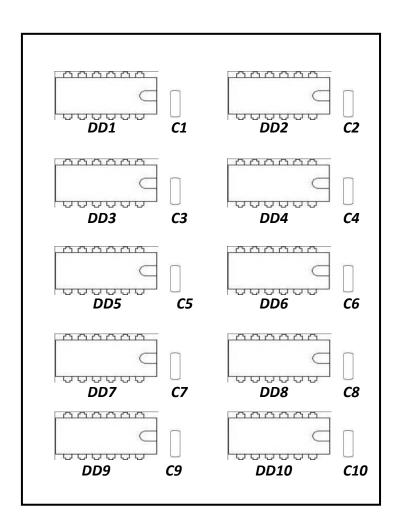

Проектируемый двоичный дешифратор 4—16 состоит из двух ИМС КР1533ЛН1, восьми ИМС КР531ЛА7 и десяти керамических конденсаторов типа КМ емкостью 0,1 мкФ.

Элементы установлены на односторонней печатной плате, изготовленной по субтрактивной технологии.

Печатная плата соответствует 3 классу плотности согласно ГОСТ 2.414-78 и имеет следующие параметры:

Материал текстолит фольгированный СФ-1H-50Г-1,2.

Шаг координатной сетки 1,27 мм

Ширина проводника t=0,254 мм

Ширина пояска печатной площадки b=0,1мм

Толщина фольги печатной платы  $h_{\phi}$ =50 мкм (без лужения)

Толщина фольги печатной платы  $h_{\phi}$ '=70 мкм (с лужением)

#### 4.4. Размещение элементов на плате.

Размещение элементов проектируемого двоичного дешифратора  $4 \rightarrow 16$  производится согласно сборочному чертежу XXXX.758710.005.XXCБ.

Конденсаторы, установленные на печатной плате должны иметь выводы минимальной длинны.

Установка и крепление микросхем на печатной плате должны обеспечивать их нормальную работу в условиях эксплуатации аппаратуры.

|         |      |                |          |          | XXXX.758710          | .002.XXЭ | 3      |        |

|---------|------|----------------|----------|----------|----------------------|----------|--------|--------|

|         | _    | W. 3           | - `      |          | Элемент базовый ТТЛШ | Лит.     | Масса  | Масшт. |

|         | Лист |                | Подпись  | Дата     | 1533 cepuu           |          |        |        |

| Разраб. |      | Романычев И.А. | <b>!</b> |          | -                    |          |        |        |

| Про     | в.   |                |          |          | схема электрическая  |          |        |        |

| Т.ко    | нтр. |                |          | <u> </u> | принципиальная       | Лист 1   | Листов | 1      |

| Н.ко    | нтр. |                |          |          |                      |          |        | 23     |

| Утв.    | -    |                |          |          |                      |          |        |        |

|      |      |                |         |      | XXXX.758710          | .003.XXЭ | 3                   |          |  |  |

|------|------|----------------|---------|------|----------------------|----------|---------------------|----------|--|--|

|      |      |                |         |      | Элемент базовый ТТЛШ | Лит.     | Масса               | Масшт.   |  |  |

| Изм  | Лист | № докум.       | Подпись | Дата |                      |          |                     |          |  |  |

| Разр | аб.  | Романычев И.А. |         |      | 531 cepuu            |          |                     |          |  |  |

| Проє | 3.   |                |         |      |                      |          | схема электрическая |          |  |  |

| Т.ко | нтр. |                |         |      | принципиальная       | Лист 1   | Листов              | Листов 1 |  |  |

|      |      |                |         |      |                      |          |                     | 24       |  |  |

| Н.ко | нтр. |                |         |      |                      |          |                     |          |  |  |

| Утв. |      |                |         |      |                      |          |                     |          |  |  |

|       |       |                |         |      | XXXX.758710        | 0.005.XXCI | 5        |                  |  |   |

|-------|-------|----------------|---------|------|--------------------|------------|----------|------------------|--|---|

|       |       |                |         |      | Размещение деталей | Лит.       | Масса    | Масшт.           |  |   |

| Изм.  | Лист  | № докум.       | Подпись | Дата | -                  |            |          |                  |  |   |

| Разр  | раб.  | Романычев И.А. |         |      | на плате печатной  |            |          |                  |  |   |

| Про   | 8.    |                |         |      | ļ                  |            |          | дешифратора 4→16 |  | ļ |

| Т. кс | нтр.  |                |         |      |                    | Лист 2     | Листов 2 |                  |  |   |

|       |       |                |         |      |                    |            |          |                  |  |   |

| Н. кс | онтр. |                |         |      |                    |            |          |                  |  |   |

| Утв   |       |                |         |      |                    |            |          |                  |  |   |

| По<br>об | з.<br>ОЗН. |                 |           | I             | Наименование       | Кол.  | Примеч                                       | <i>нание</i> |

|----------|------------|-----------------|-----------|---------------|--------------------|-------|----------------------------------------------|--------------|

|          |            |                 |           |               |                    |       |                                              |              |

|          |            |                 |           | <u>Cr</u>     | <u>пецификация</u> | 1     | лист                                         |              |

|          |            |                 |           | Chor          | очный чертеж       |       |                                              |              |

|          |            | XXXX.758        | 710 005 \ | 2             | лист               |       |                                              |              |

|          |            | 70000.700       | 110100012 | _             | , aom              |       |                                              |              |

|          |            |                 |           | очная единица |                    |       |                                              |              |

|          |            | Дешифра         | mop 4→1   | 6             |                    | 1     | шт.                                          |              |

|          |            |                 |           |               |                    |       |                                              |              |

|          |            |                 |           |               | <u>Детали</u>      |       |                                              |              |

|          |            | Плата печ       | натная о  | дносп         | поронняя           | 1     | шт.                                          |              |

|          |            |                 |           |               |                    |       |                                              |              |

|          |            |                 |           | <u>N</u>      | <u> Иикросхемы</u> |       |                                              |              |

| DD       | 1,DD2      | <b>КР1533ЛН</b> | 11        | 2             | шт.                |       |                                              |              |

| DD3      | 8,DD10     | КР531ЛА7        | ,         |               |                    | 8     | шт.                                          |              |

|          |            |                 |           |               |                    |       |                                              |              |

|          |            |                 |           | <u>Ko</u>     | <u>нденсаторы</u>  |       |                                              |              |

| C1-      | -C10       | КМ 0,1 мкФ      | <b>)</b>  | 10            | шт.                |       |                                              |              |

|          |            |                 |           |               |                    |       |                                              |              |

|          |            |                 |           |               |                    |       |                                              |              |

|          |            | _               |           |               |                    |       |                                              |              |

|          |            |                 |           |               |                    |       |                                              |              |

|          |            |                 |           |               |                    |       |                                              |              |

|          |            |                 |           |               |                    |       |                                              |              |

|          |            |                 |           |               |                    |       |                                              |              |

|          |            |                 |           |               |                    |       |                                              |              |

|          |            |                 |           |               |                    |       |                                              |              |

|          |            | •               |           |               | VVVV 750740 A      | NE VV | <u>.                                    </u> |              |

|          | Лист       | № докум.        | Подпись   | Дата          | XXXX.758710.0      |       |                                              |              |

| Разра    |            | Романычев И.А.  |           |               | Дешифратор 4→16    |       | ит. Лист                                     | Листов       |

| Пров.    |            |                 |           |               | перечень элементов |       | y 1                                          | 1            |

| Н. кон   |            |                 |           |               |                    |       |                                              | 27           |

| Утв.     |            |                 |           |               |                    |       |                                              |              |

### СПИСОК ИСПОЛЬЗУЕМОЙ ЛИТЕРАТУРЫ

- 1.Потемкин И.С. *Функциональные узлы цифровой автоматики.* М.:Энергоатомиздат, 1988-320с.

- 2.Угрюмов Е.П. **Цифровая схемотехника**. СПб.:БХВ-Петербург, 2001 -528с.

- 3.Угрюмов Е.П. *Проектирование элементов и узлов ЭВМ.* М.:Высшая школа, 1987-318с.

- 4.Шило В.Л. *Популярные цифровые микросхемы.* М.:Радио и связь, 1989-352с.

- 5.Тарабрин Б.В. *Интегральные микросхемы*. М.: Энергоатомиздат, 1985-528c.

- 6. Хоровиц П., Хилл У. *Искусство схемотехники*. *Часть 2*. М.: Мир, 1993-371с.

- 7.Мальцев П.П., Долидзе Н.С. и др. **Цифровые интегральные микросхемы: Справочник**. М.:Радио и связь, 1994-240с.

- 8. Тарабрин Б.В., Якубовский С.В., Барканов Н.А. и др. *Справочник по интегральным микросхемам.* М.: Энергия, 1980-816с.